Bộ vi xử lý P1020NXN2HFB – MPU 800/400/667 ET NE r1.1

♠ Mô tả sản phẩm

| Thuộc tính sản phẩm | Giá trị thuộc tính |

| Nhà sản xuất: | NXP |

| Danh mục sản phẩm: | Bộ vi xử lý - MPU |

| RoHS: | Chi tiết |

| Kiểu lắp đặt: | SMD/SMT |

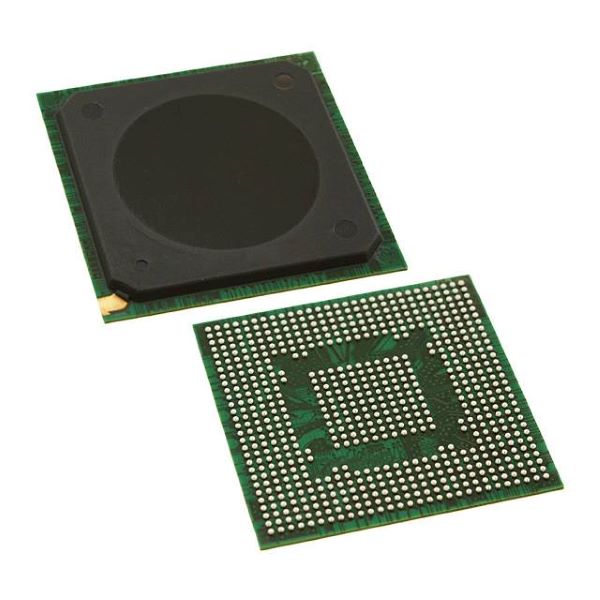

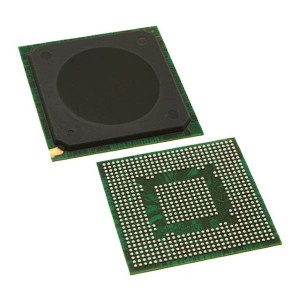

| Gói/Hộp: | TEPBGA-689 |

| Loạt: | P1020 |

| Cốt lõi: | e500 |

| Số lượng lõi: | 2 Lõi |

| Chiều rộng bus dữ liệu: | 32 bit |

| Tần số xung nhịp tối đa: | 800MHz |

| Bộ nhớ lệnh đệm L1: | 2x32kB |

| Bộ nhớ dữ liệu đệm L1: | 2x32kB |

| Điện áp cung cấp hoạt động: | 1 năm |

| Nhiệt độ hoạt động tối thiểu: | - 40 độ C |

| Nhiệt độ hoạt động tối đa: | + 125 độ C |

| Bao bì: | Khay |

| Thương hiệu: | Chất bán dẫn NXP |

| Điện áp I/O: | 1,5V, 1,8V, 2,5V, 3,3V |

| Loại hướng dẫn: | Điểm nổi |

| Loại giao diện: | Ethernet, I2C, PCIe, SPI, UART, USB |

| Bộ nhớ đệm hướng dẫn/dữ liệu L2: | 256kB |

| Kiểu bộ nhớ: | Bộ nhớ đệm L1/L2 |

| Nhạy cảm với độ ẩm: | Đúng |

| Số lượng I/O: | 16 Đầu vào/Đầu ra |

| Dòng bộ xử lý: | Tiếng Việt |

| Loại sản phẩm: | Bộ vi xử lý - MPU |

| Số lượng đóng gói tại nhà máy: | 27 |

| Tiểu thể loại: | Bộ vi xử lý - MPU |

| Tên thương mại: | Tiếng Việt |

| Bộ đếm thời gian giám sát: | Không có bộ đếm thời gian giám sát |

| Phần # Biệt danh: | 935310441557 |

| Đơn vị Trọng lượng: | 5,247 gam |

• Lõi 32-bit hiệu suất cao kép, được xây dựng trên công nghệ Power Architecture®:

– Địa chỉ vật lý 36 bit

– Hỗ trợ dấu phẩy động độ chính xác kép

– Bộ nhớ đệm lệnh L1 32 Kbyte và bộ nhớ đệm dữ liệu L1 32 Kbyte cho mỗi lõi

– Tần số xung nhịp 533 MHz đến 800 MHz

• Bộ nhớ đệm L2 256 Kbyte với ECC. Cũng có thể cấu hình như SRAM và bộ nhớ đệm.

• Ba bộ điều khiển Ethernet ba tốc độ nâng cao 10/100/1000 Mbps (eTSEC)

– Tăng tốc TCP/IP, chất lượng dịch vụ và khả năng phân loại

– Hỗ trợ IEEE® 1588

– Kiểm soát lưu lượng không mất mát

– MII, RMII, RGMII, SGMII

• Giao diện tốc độ cao hỗ trợ nhiều tùy chọn ghép kênh khác nhau:

– Bốn SerDes lên đến 2,5 GHz/làn được ghép kênh trên các bộ điều khiển

– Hai giao diện PCI Express

– Hai giao diện SGMII

• Bộ điều khiển USB tốc độ cao (USB 2.0)

– Hỗ trợ máy chủ và thiết bị

– Giao diện bộ điều khiển máy chủ nâng cao (EHCI)

– Giao diện ULPI với PHY

• Bộ điều khiển máy chủ kỹ thuật số an toàn nâng cao (SD/MMC)

• Giao diện ngoại vi nối tiếp nâng cao (eSPI)

• Công cụ bảo mật tích hợp

– Hỗ trợ giao thức bao gồm ARC4, 3DES, AES, RSA/ECC, RNG, SSL/TLS một lần

– Tăng tốc XOR

• Bộ điều khiển bộ nhớ SDRAM DDR2/DDR3 32-bit có hỗ trợ ECC

• Bộ điều khiển ngắt có thể lập trình (PIC) tuân thủ tiêu chuẩn OpenPIC

• Một bộ điều khiển DMA bốn kênh

• Hai bộ điều khiển I2 C, DUART, bộ hẹn giờ

• Bộ điều khiển bus cục bộ nâng cao (eLBC)

• TDM

• 16 tín hiệu I/O mục đích chung

• Phạm vi nhiệt độ mối nối hoạt động (Tj): 0–125°C và –40°C đến 125°C (thông số kỹ thuật công nghiệp)

• 31 × 31 mm 689 chân WB-TePBGA II (nhựa BGA tăng cường nhiệt độ liên kết dây)